## 6 Estudos de Casos

Com o objetivo de avaliar a síntese automática de circuitos de QCA usando técnicas de Hardware Evolucionário (EHW), alguns circuitos foram sintetizados e serão apresentados a seguir. As simulações de todos os circuitos sintetizados estão no apêndice 3.

### 6.1. Porta Lógica OU de 4 Entradas

Este experimento pretende sintetizar uma porta lógica OU com quatro entradas. O objetivo é encontrar uma porta lógica que funcione corretamente, além de possuir o menor número de células possível. Circuitos com menos células são mais rápidos e têm uma tendência menor de apresentarem defeitos.

Este experimento utilizou somente células convencionais, logo o modelo coevolucionário cooperativo genético possui apenas duas populações, uma responsável pela topologia do circuito e outra pela zona de *clock* das células, não sendo necessário o cromossoma que define o tipo da célula.

A função de avaliação para este circuito foi baseada no número de acertos da porta lógica para as 16 possíveis configurações de entrada cuja saída desejada é igual ao binário 0 somente uma vez, considerando todo o conjunto de entradas. Logo, esta saída específica tem peso dois para que se possa ajudar a evolução. Somando-se todas as outras saídas possíveis, a avaliação total do circuito com a lógica 100% correta é igual a 17 (15 saídas desejadas com o binário 1 e uma saída desejada, de peso dois, com o binário 0).

Sempre que um circuito atinge a pontuação máxima (neste caso 17), ele recebe um bônus relativo à quantidade de células presentes. Como, neste caso, a grade utilizada permite um número máximo de trinta e cinco células, o bônus foi definido como trinta dividido pelo número de células no circuito. Assim, quanto menos células no circuito melhor a avaliação. O valor do bônus foi definido de

acordo com observações de experimentos anteriores, onde a grande maioria dos circuitos criados com a lógica correta possuía menos que trinta células.

A equação abaixo representa a função de avaliação de um circuito com a lógica correta. Circuitos que não têm a lógica 100% correta não possuem o último termo da função de avaliação:

Avaliação = Acertos(Binário 1) +  $2 \times Acertos(Binário 0) + 30/\# células$  (9)

O circuito evoluído possui quatro células de entrada, uma célula com o valor fixo no binário 1 e uma célula de saída. A definição da posição destas células foi baseada em circuitos previamente existentes ou em testes anteriores.

Os parâmetros do Algoritmo Genético utilizado neste experimento estão especificados abaixo:

| • | Gerações: | 200; |

|---|-----------|------|

|---|-----------|------|

• População: 50;

• Taxa inicial de *crossover*: 0,9;

• Taxa final de *crossover*: 0.75;

• Taxa inicial de mutação: 0,2;

• Taxa final de mutação: 0,5;

• *Steady State*: 0,2.

Sendo este circuito simples e a grade utilizada razoavelmente pequena, a evolução não é muito difícil. Mesmo assim o Algoritmo Genético mostrou bons resultados se comparado com a busca aleatória e com o circuito fornecido por um especialista. A tabela 5 mostra o número de experimentos que geraram circuitos com a lógica correta, o número médio de células no menor circuito com a lógica correta e o número de células no menor circuito encontrado. Um total de 10 experimentos foram executados.

|           | Número de experimentos com a lógica correta | Número médio de<br>células nos circuitos<br>corretos | Número de células no melhor circuito encontrado |

|-----------|---------------------------------------------|------------------------------------------------------|-------------------------------------------------|

| Aleatório | 7                                           | 20.28                                                | 16                                              |

| GA        | 10                                          | 15.8                                                 | 12                                              |

Tabela 5- Comparação dos dados de 10 experimentos.

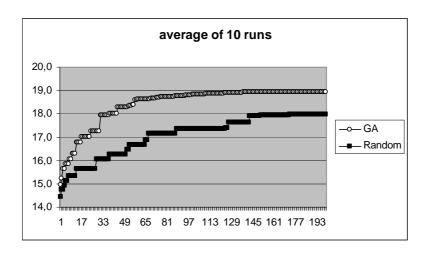

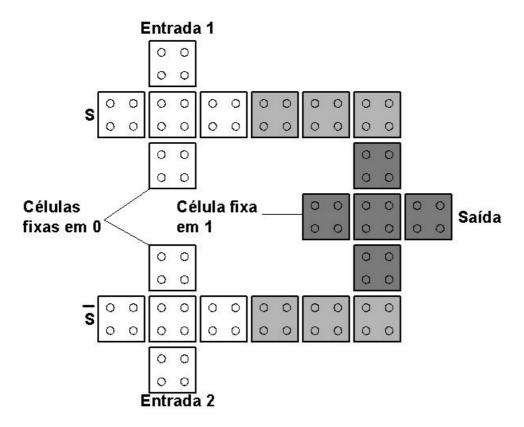

Figura 32- Média dos melhores indivíduos por geração.

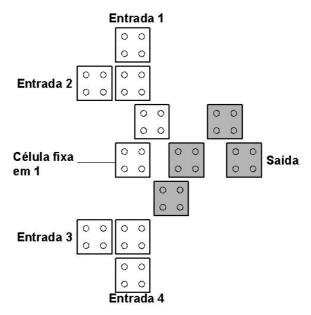

Observe que o AG encontrou circuitos com a lógica correta em todos os experimentos, otimizando-os. A figura 33 ilustra a topologia do melhor circuito encontrado pelo AG, com 12 células, e a figura 34 ilustra a topologia da porta lógica OU apresentada em [84], com 18 células. Os tons de cinza representam as zonas de *clock*. Logo, o modelo de síntese automática de circuitos de QCA, sugerido nesta dissertação, foi capaz de encontrar um circuito 33% menor.

Figura 33- Melhor circuito OU de quatro entradas evoluído pelo AG.

Figura 34 – Circuito OU proposto na literatura.

Os circuitos apresentados acima possuem topologias bem diferentes. O circuito apresentado em [84] foi criado por um especialista que explora a disponibilidade de usar portas lógicas OU de duas entradas para a construção de portas lógicas OU de quatro entradas. Ao contrário, a única informação fornecida para a síntese evolucionária foi o posicionamento das células de entrada, da célula fixa e da célula de saída. Para um especialista é mais fácil projetar circuitos utilizando *majority gates*, enquanto que a síntese automática é livre para criar novas topologias inimagináveis pelos especialistas.

Para a síntese automática desta porta lógica, um *grid* de três Pentium 4 2.2GHz rodando em paralelo foi usado. Um destes computadores controla também o AG e distribui a simulação para os outros computadores. O tempo necessário para que dez rodadas fossem realizadas foi de pouco mais que três horas.

O circuito da porta lógica E com quatro entradas é semelhante a estes, com apenas uma alteração: substituir as células fixas com o binário 1 para células fixas com o binário 0.

# 6.2. Multiplexador

O objetivo deste próximo experimento é sintetizar um multiplexador de duas entradas e com o menor número possível de células. Uma terceira entrada é utilizada como sinal de seleção do multiplexador. Como no experimento anterior, somente células convencionais são usadas, logo somente dois cromossomos são necessários. Para a síntese automática de um multiplexador, um grid de três Pentium 4 2.2GHz rodando em paralelo foi usado, tal como no experimento anterior. O tempo necessário para a execução de dez rodadas foi de pouco menos que sete horas e, neste caso, mais de oitenta mil soluções foram avaliadas.

A função de avaliação para este circuito foi baseada no número de acertos da porta lógica, para todas as 8 possíveis configurações de entradas. Porém, neste caso uma penalidade é aplicada aos indivíduos (soluções) que cometam erros quando a saída desejada é igual ao binário 0, com o objetivo de evitar que o AG fique preso em um mínimo local, já que o multiplexador funciona como uma soma de produtos, conforme explicado anteriormente no capítulo 5. Sempre que um circuito atinge a lógica correta, ele recebe uma bonificação referente à quantidade de células no circuito. Para este experimento o bônus foi determinado exatamente como no experimento anterior.

O circuito evoluído possui quatro células de entrada (duas destas células são usadas pelo *bit* de seleção), uma célula de saída e duas células fixas (uma fixa com o binário 0 e outra fixa com o binário 1). A posição das células foi baseada na configuração de circuitos conhecidos.

Os parâmetros do Algoritmo Genético são os seguintes:

| • | Gerações:                  | 200; |

|---|----------------------------|------|

| • | População:                 | 100; |

| • | Taxa inicial de crossover: | 0,9; |

| • | Taxa final de crossover:   | 0,75 |

| • | Taxa inicial de mutação:   | 0,2; |

| • | Taxa final de mutação:     | 0,5; |

| • | Steady State:              | 0,2. |

Novamente, o Algoritmo Genético apresentou bons resultados se comparado com a busca aleatória. A tabela 6 mostra o número de experimentos que geraram

circuitos com lógica correta, o número médio de células nos circuitos corretos e o número de células no melhor circuito encontrado. Um total de 10 experimentos foi executado.

|           | Número de        | Número médio de       | Número de       |

|-----------|------------------|-----------------------|-----------------|

|           | experimentos com | células nos circuitos | células no      |

|           | a lógica correta | corretos              | melhor circuito |

| Aleatório | 4                | 21                    | 20              |

| AG        | 9                | 17                    | 14              |

Tabela 6- Comparação dos dados de 10 experimentos.

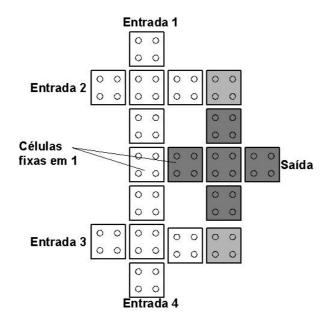

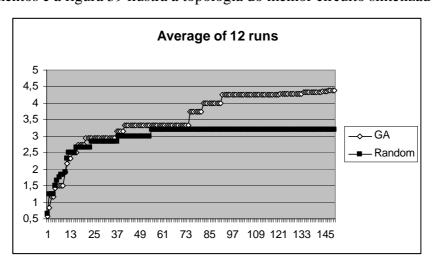

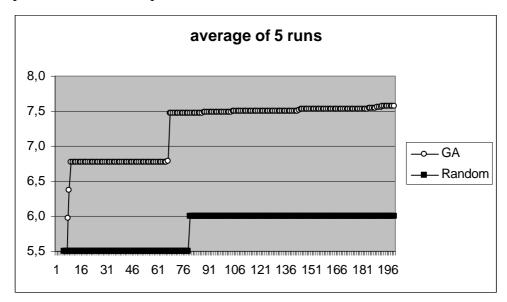

O gráfico da evolução pode ser observado na figura 35, que mostra a média dos melhores indivíduos por geração, em um total de 10 experimentos de 200 gerações. O eixo vertical representa a avaliação do indivíduo. A avaliação mínima de um circuito com a lógica correta é igual a oito. Observe que o AG encontra, em média, circuitos com a lógica correta a partir da geração quarenta e cinco. A figura 36 mostra a topologia do melhor circuito encontrado pela metodologia proposta, contendo 14 células. Os tons de cinza representam as zonas de *clock*.

Figura 35– Média dos melhores indivíduos por geração.

Figura 36— **Topologia do melhor multiplexador encontrado pelo AG,** contendo 14 células. Os tons de cinza representam as zonas de *clock*.

Para fins de comparação, a figura 37 apresenta a topologia do multiplexador considerado por Niemier [50], com 21 células. O circuito sintetizado pela técnica proposta neste trabalho é menor e mais compacto. Estas características são importantes em circuitos de QCA. Circuitos menores possuem a vantagem de serem mais rápidos e com grande probabilidade de funcionarem de maneira correta, evitando os efeitos termodinâmicos discutidos por Lent [3]. Além disso, circuitos mais compactos permitem criar circuitos mais densos, usando menos espaço para o desenvolvimento de topologias lógicas.

Figura 37 – **Topologia do multiplexador sugerido por Lent, contendo 21** células. Os tons de cinza representam as zonas de *clock*.

Com o intuito de aumentar a complexidade da evolução, o espaço de busca foi aumentado de uma grade de 13x9 para uma grade de 13x13. Neste caso, a busca aleatória não encontrou nenhum circuito com a lógica correta. Por outro lado, o AG continuou sintetizando os circuitos desejados em 60% dos experimentos.

### 6.3. Ou-exclusivo

Este experimento tem como objetivo sintetizar um circuito Ou-exclusivo (XOR) através de técnicas evolucionárias. O XOR é uma função não-linearmente separável, logo sua síntese não é trivial. Como nos experimentos anteriores, a metodologia proposta foi capaz de sintetizar circuitos com a lógica correta.

Ao contrário dos dois experimentos anteriores, neste o modelo coevolucionário genérico possui três populações, já que o tipo da célula também é necessário ser evoluído. Com o intuito de executar este experimento, dezessete computadores Pentium 4 2.2GHz, em um *grid*, foram usados. Como nos experimentos anteriores, um computador, além de executar simulações, controla o AG e distribui os indivíduos para serem simulados nos demais computadores. Esta distribuição permite uma otimização do tempo de execução do experimento. Neste caso, computadores mais rápidos recebem mais indivíduos para serem simulados. O tempo necessário para as 12 rodadas foi de aproximadamente 12 horas (em média, uma hora para cada experimento). Neste caso, mais de cento e dez mil soluções foram avaliadas.

Os parâmetros do Algoritmo Genético estão apresentados abaixo:

| • | Gerações:                  | 150;  |

|---|----------------------------|-------|

| • | População:                 | 200;  |

| • | Taxa inicial de crossover: | 0,9;  |

| • | Taxa final de crossover:   | 0,65; |

| • | Taxa inicial de mutação:   | 0,2;  |

| • | Taxa final de mutação:     | 0,4;  |

| • | Steady State:              | 0.2.  |

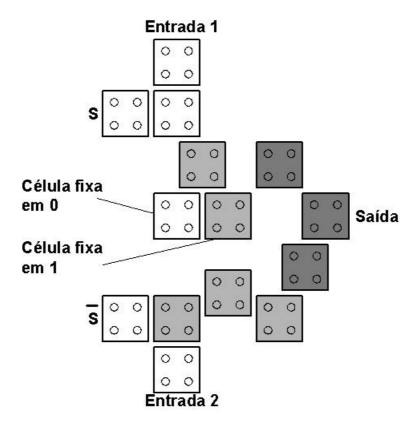

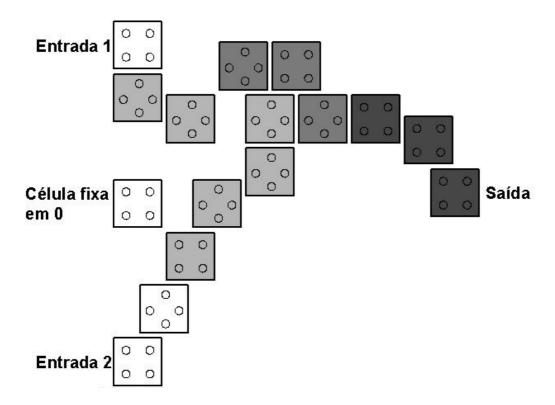

A figura 38 apresenta o gráfico da evolução para um total de 12 experimentos e a figura 39 ilustra a topologia do melhor circuito sintetizado.

Figura 38- Média dos melhores indivíduos por geração.

Figura 39- Topologia do melhor Ou-exclusivo encontrado pelo AG. Os tons de cinza representam as zonas de *clock*.

A figura 40 abaixo ilustra a topologia do XOR proposto em [2]. Além de extremamente grande, este circuito não considerava as zonas de *clock*, o que o torna inviável do ponto de vista funcional.

Figura 40- Topologia do Ou-exclusivo proposto na literatura.

Esta nova topologia da porta lógica XOR enfatiza a eficiência da síntese evolucionária no desenvolvimento de circuitos menores. Normalmente, especialistas utilizam células rotacionadas para transmitir a informação, raramente para a criação de lógica. A síntese automática proposta nesta dissertação permite explorar células rotacionadas, usando-as juntamente com as células convencionais na construção de circuitos lógicos. O circuito encontrado possui menos de um terço do número de células do que o circuito da literatura.

O circuito evoluído possui quatro células fixas definidas pelo usuário, duas células de entrada, uma célula de saída e uma célula fixada com o binário 0. A definição da posição destas células foi baseada em testes anteriores.

A técnica proposta nesta dissertação encontrou circuitos com a lógica correta na maioria dos experimentos, enquanto a busca aleatória obteve sucesso em apenas um dos 12 experimentos executados.

# 6.4. Somador Completo

O objetivo deste último experimento é sintetizar automaticamente um circuito de QCA complexo. Para isso, foi escolhida a síntese de um somador completo, um dos maiores circuitos lógicos de QCA desenvolvidos na literatura. Espera-se que, como nos experimentos anteriores, a síntese automática deste somador completo seja capaz de encontrar um circuito menor que o existente na literatura. Um desafio para a síntese automática deste circuito é que o somador da literatura possui um total de 145 células em uma grade de 43x35. Sendo assim, cada cromossomo teria um tamanho total de 1477, já descontando as posições de entrada e saída. Este valor torna a síntese automática quase inviável. Considerando que as primeiras 14 colunas da grade são usadas somente para o fluxo dos sinais de entrada e que o restante é usado pela parte lógica, a síntese pode utilizar uma grade de 43x21, o que reduz o tamanho total de cada cromossomo para 849. Ainda assim é um tamanho bastante considerável, dificultando a síntese do novo circuito.

Logo, para que a síntese do somador completo fosse viável, duas alternativas foram desenvolvidas e serão mostradas a seguir.

## 6.4.1. Alternativa 1

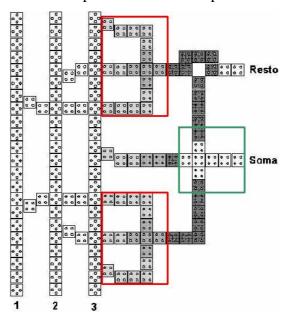

A primeira alternativa propõe a otimização dos *Majority Gates* utilizados no somador. A figura 41 abaixo ilustra a topologia do somador completo encontrado na literatura [85]. As partes marcadas na figura foram sintetizadas automaticamente com o objetivo de diminuir o número de células. A figura 42 mostra a topologia do circuito após a síntese destas partes.

Figura 41— **Topologia do somador completo. Partes vermelhas e verdes** serão substituídas por partes menores.

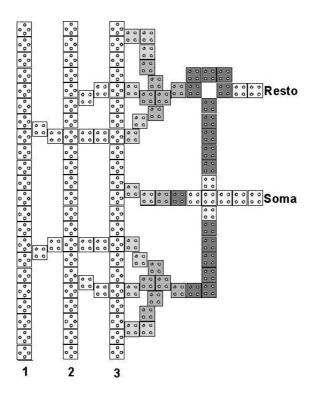

Figura 42- Topologia do novo circuito do somador completo.

As partes marcadas com vermelho na figura 41 foram substituídas por dois novos circuitos. Apenas uma destas partes foi sintetizada. A outra parte foi adaptada, já que sua forma é bem semelhante e foi necessária a inclusão de apenas uma célula. A parte marcada com a cor verde também foi sintetizada, mas o resultado não foi melhor do que o existente na figura 41, que já é o circuito ótimo. Logo, esta parte do circuito foi mantida como a original.

A colocação dos novos circuitos sintetizados diminuiu a quantidade de células e ainda permitiu uma diminuição no número de colunas horizontais do circuito. Com isso, o novo circuito possui 15 células a menos que o antigo, passando a ter 130 células, uma diminuição de aproximadamente 10%.

Os parâmetros do AG usado foram:

| • | Gerações:                  | 100; |

|---|----------------------------|------|

| • | População:                 | 50;  |

| • | Taxa inicial de crossover: | 0,9; |

| • | Taxa final de crossover:   | 0,5; |

| • | Taxa inicial de mutação:   | 0,3; |

| • | Taxa final de mutação:     | 0,7; |

#### • Steady State:

0,2.

A tabela 7 abaixo mostra a comparação entre a busca aleatória e a síntese automática utilizando algoritmos genéticos em um total de 10 experimentos.

|           | Número de        | Número médio de       | Número de       |

|-----------|------------------|-----------------------|-----------------|

|           | experimentos com | células nos circuitos | células no      |

|           | a lógica correta | corretos              | melhor circuito |

| Aleatório | 8                | 18,78                 | 16              |

| AG        | 9                | 16,22                 | 12              |

Tabela 7 – Comparação entre a busca aleatória e o AG.

Este resultado mostra que este circuito não é tão difícil de ser encontrado, mas mesmo assim a síntese automática utilizando um AG encontrou um circuito 25% menor que o melhor circuito encontrado pela busca aleatória.

### 6.4.2. Alternativa 2

Esta alternativa foi proposta com o objetivo de diminuir ainda mais o tamanho do circuito do somador completo.

Aqui, as duas partes principais do circuito serão sintetizadas separadamente. A primeira parte é o circuito que calcula o resto da soma de três números. A lógica deste circuito é exatamente a mesma que a lógica evoluída na alternativa 1, ou seja, não é necessário refazer a síntese.

A segunda parte consiste em sintetizar a parte da soma. Para isto foi utilizada uma grade de 13x21. Os parâmetros do AG são mostrados abaixo:

| • | Gerações:                  | 400; |

|---|----------------------------|------|

| • | População:                 | 200; |

| • | Taxa inicial de crossover: | 0,9; |

| • | Taxa final de crossover:   | 0,65 |

| • | Taxa inicial de mutação:   | 0,3; |

| • | Taxa final de mutação:     | 0,6; |

| • | Steady State:              | 0,2. |

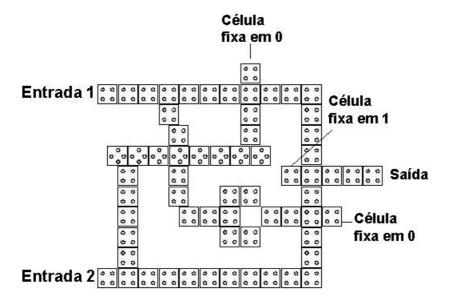

A figura 43 abaixo mostra as curvas de evolução da técnica utilizando o modelo proposto nesta dissertação e a busca aleatória. O resultado da técnica proposta é claramente superior.

Figura 43- Média dos melhores indivíduos por geração.

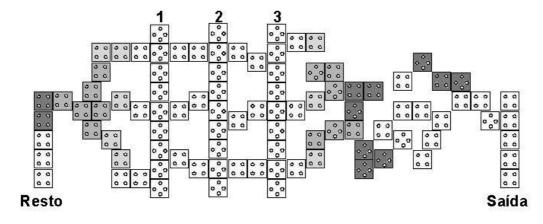

A figura 44 apresenta a topologia do novo somador.

Figura 44- Topologia do novo somador completo.

Este novo circuito contém 96 células. Isto significa uma redução de aproximadamente 34% na quantidade de células em relação ao circuito sugerido em [85] e uma redução de 26% em relação ao circuito proposto na alternativa 1.

A vantagem de sintetizar separadamente essas duas partes do circuito permite que elas funcionem de forma independente. Com isso foi possível colocar a parte da soma à direita das entradas e a parte do resto à esquerda das entradas.

O novo somador comprova a vantagem das técnicas inteligentes, que exploraram as células rotacionadas para a construção da lógica, e não somente para a distribuição do sinal, permitindo a criação de topologias inovadoras.

Cada um dos cinco experimentos demorou, em média, oito horas, sendo necessário quarenta horas para a execução de todos eles experimentos.

Aqui um *grid* de 10 Pentium 2.2GHz foi usado para a execução dos experimentos. Um computador ficou responsável apenas pelo AG, enquanto os outros nove ficaram responsáveis pelas simulações dos circuitos.

A seguir a conclusão final desta dissertação e os trabalhos futuros sugeridos serão apresentados.